IC Packaging Design and Simulation Services

Moore's Law is approaching its limit. From the perspective of packaging, Chiplet is one of the main technological paths to go beyond Moore's Law. It packages different chips side by side or in a stacked manner, integrating multiple IPs with different functions and passive components together through advanced packaging technologies to form a single standard package with certain functions. Constrained by the limit of Moore's Law, the number of components that can be integrated per unit area is getting closer and closer to the physical limit. However, Chiplet packaging technology can achieve a higher level of integration, and the combined system has better performance, making it an inevitable choice to surpass Moore's Law.

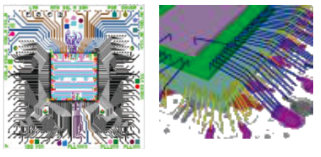

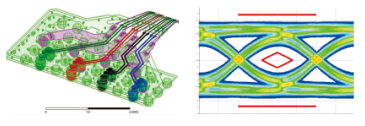

Packaging Design Packaging design; IC carrier board design; COB/COF design...

| Electrical Simulation Moore's Law is approaching its limit, and Chiplet, starting from the perspective of packaging, is the main technological path beyond Moore's Law in packaging electrical simulation, with pre simulation and post simulation of packaging RLC parameters and S parameter extraction; Package power integrity simulation; Encapsulation signal integrity simulation; PKG and PCB joint simulation.

|

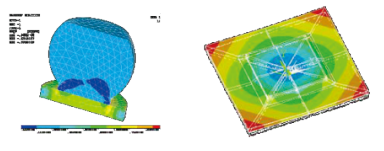

Stress Simulation Package Warpage Simulation; Thermal Stress Simulation and Optimization; Solder Joint Fatigue Life Analysis.

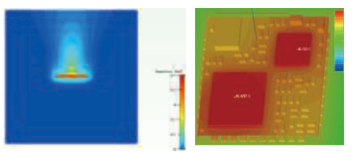

| Thermal Simulation Extraction of packaging thermal models; Thermal simulation of packaging under JEDEC or actual system environments; Optimization of packaging thermal management.

|